CoCoVGA SAM Accelerator

The CoCoVGA SAM accelerator hardware plugs into the SAM chip socket and enables true double-speed functionality on a CoCo 1 or 2 when accessing both ROM and RAM. This hardware requires version 0.92 or later of the CoCoVGA FPGA. See also Ed Snider's page at https://thezippsterzone.com/2019/04/04/cocovga-sam-accelerator/.

Hardware Requirements

The CoCoVGA SAM accelerator requires CoCoVGA main FPGA version 0.92 or later. The version of the FPGA is momentarily shown in the border at power-on of your CoCo. For information on upgrading your CoCoVGA FPGA, see FPGA Update.

On some systems, it seems that new, faster, PIA (6821) or RAM chips are not necessary to support the SAM accelerator's true double speed mode.

In the case of flickering or garbled CoCoVGA video output, faster PIAs such as the HD68B21P may be needed. Color Computer systems have two of these.PIAs.

For the purposes of checking your RAMs' speed, install the SAM accelerator, issue the high speed poke and then run a test program such as the Color Computer 64 Memory Test. If faster RAM chips are required, chips that should work better include 4164B-12 and 41464C-10, depending on the type of Color Computer.

Known Issues

Currently, the SAM accelerator is incompatible with real floppy drive controllers, no matter whether overclocking is enabled or not. Users have experienced corrrupted disk reads with real floppy drives, Gotek drives, and with Tandy and J&M controllers. It may also affect real hard drive controllers. It is functioning reliably with the CoCoSDC, however.

Troubleshooting

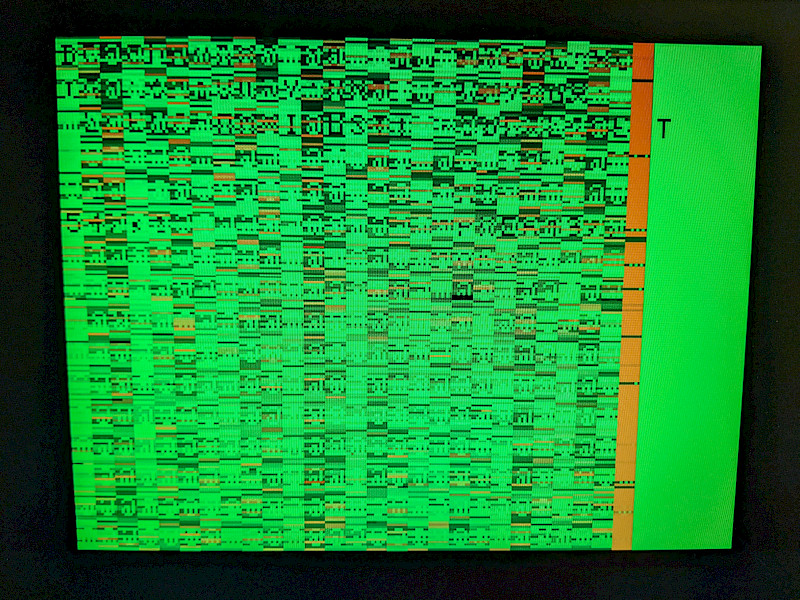

Garbled video such as this:

may imply that you have not updated your CoCoVGA FPGA to version 0.92 or later. See FPGA Update.

Installation

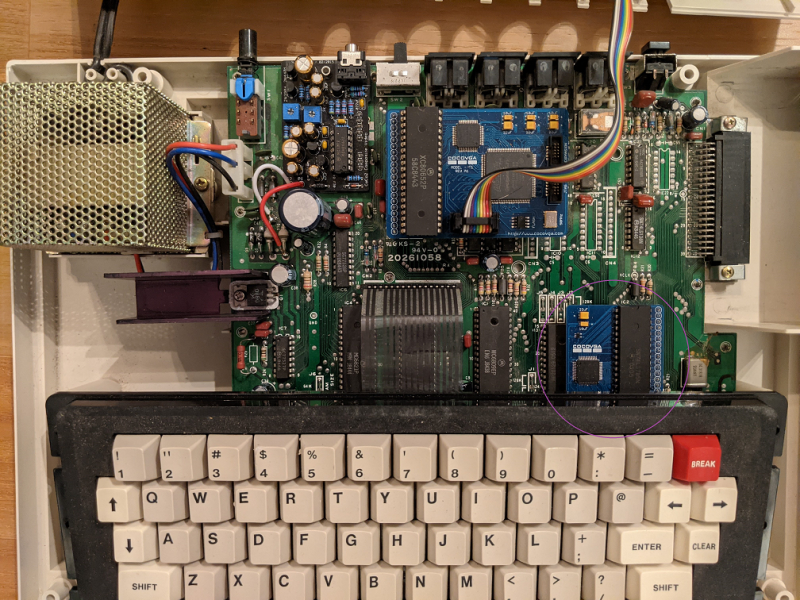

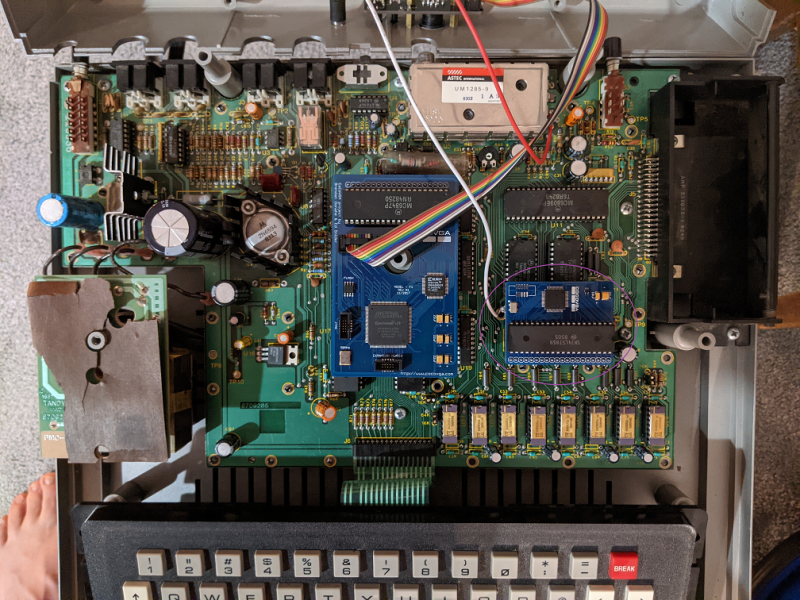

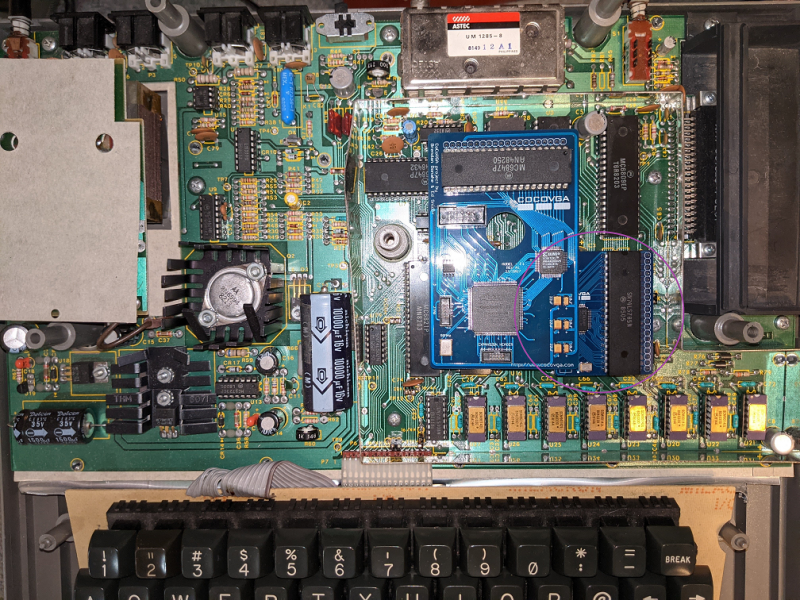

The photos below depict 4 different Color Computers, each with both a CoCoVGA and a SAM Accelerator installed. The SAM Accelerator is circled in purple. This is provided as a reference for those who may have other boards in their systems which could interfere with installation.

Korean-made NTSC Color Computer 2 (horizontal RF can)

Note that in this system, the keyboard rests on and applies a bit of pressure to the SAM Accelerator.

American-made "rev B" Color Computer 2 (vertical RF can)

Rev F Color Computer 1 or TDP-100

Rev E Color Computer 1

In this photo, the approximate location of a CoCoVGA board intended for a rev F CoCo 1 after shifting it to the right with an adapter board is shown. Given the additional height of the adapter board, the SAM Accelerator should fit underneath the CoCoVGA board.

Theory of Operation

The SAM (Synchronous Address Multiplexer - 6883/74LS783 or 74LS785), as used in the Color Computer 1 and 2, has the responsibility of:

- Dividing the XTAL frequency to clock frequencies usable by the 6809 CPU and 6847 VDG (Video Display Generator)

- Multiplexing CPU and VDG accesses to RAM and ROM

- DRAM refresh

Given a 14.31818MHz input from a crystal, it provides 3 different clock frequency modes:

|

SAM CPU clocking mode |

Comments |

BASIC pokes to select mode |

6809 CPU clock frequency |

6847 VDG clock frequency |

|---|---|---|---|---|

|

Slow /16 |

Default power-on/reset mode |

POKE &HFFD8,1 or POKE 65496,1 |

0.89MHz |

3.58MHz |

|

Address Dependent /16 or /8 |

CPU clock frequency varies depending on whether access is to RAM (slow) or ROM (fast) |

POKE &HFFD7,1 or POKE 65495,1 |

0.89MHz or 1.78MHz |

3.58MHz |

|

Fast /8 |

DRAM refresh and multiplexing with VDG non-operational, resulting in scrambled video display |

POKE &HFFD9,1 or POKE 65497,1 |

1.78MHz |

3.58MHz |

The CoCoVGA SAM accelerator resolves the downsides of the “Fast” mode described in the table above by intercepting the clocking mode register writes and instead of allowing the SAM to alter its clock divider and muxing, it doubles the crystal input frequency to the SAM. The SAM continues to mux between the CPU and VDG normally and perform DRAM refresh as it would in “Slow” mode.

This also means that from a user’s perspective there is no longer any difference between the “Address Dependent” and “Fast” modes, other than the 6847 VDG’s doubled horizontal and vertical sync interrupt rate.

|

SAM CPU clocking mode |

Comments |

BASIC pokes to select mode |

6809 CPU clock frequency |

6847 VDG clock frequency |

|

Slow /16 |

Default power-on/reset mode |

POKE &HFFD8,1 or POKE 65496,1 |

0.89MHz |

3.58MHz |

|

Slow /16 but with double- frequency input clock |

Clock input to SAM is doubled from 14.31818MHz to 28.63636MHz |

POKE &HFFD7,1 or POKE &HFFD9,1 or POKE 65495,1 or POKE 65497,1 |

1.78MHz |

7.16MHz |

As alluded to earlier, note that the VDG clock frequency is also doubled in the table above. Normally, this would result in loss of video - that is, the connected TV or monitor would no longer be able to sync at this frequency. Because CoCoVGA has its own crystal for driving VGA output and because it buffers entire frames of video, it can still properly display the video with a 60Hz VGA-spec refresh rate despite the now nearly 120Hz field sync rate of the 6847 VDG.

This upgrade requires DRAM which is capable of 150ns (or faster) operation and may also need 2MHz PIAs.

This enhancement was designed and manufactured by Ed Snider with CoCoVGA FPGA support from Brendan Donahe.